Check the modified blocks with a test-bench. If the receiver de-asserts this line, the transmitter will keep (freeze) the last bit sent on the line, until the ‘receiver ready’ signal is asserted again.

SERIAL PARALLEL CONVERTER CIRCUIT FSM SERIAL

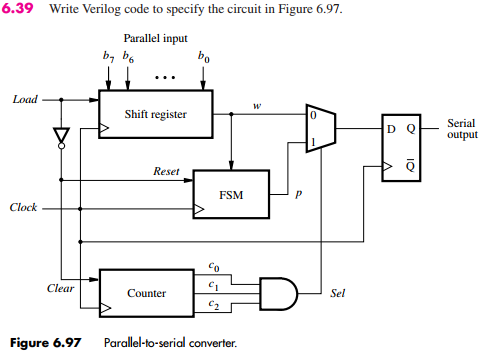

The TxD line, pin 3, CTS line, pin 8 and the DSR line, pin 6, of the serial port are used - see diagram. It converts a serial 2400 baud signal into a parallel signal. Modify both blocks and test them with a modified test-bench. This converter may help if just the serial port on a personal computer is free, whereas the printer needs a parallel (Centronics) port. Introduction For this lab, you are required to write an FSMD vhdl description of a parallel to serial converter and a testbench to show its correctness. The Parallel to serial converter will sample this line and will start a new transmission only if this line is asserted. FSM Design: Parallel to Serial Convertor I. Add a ‘receiver ready’ line, as an output from the Serial to parallel converter.

On the waveform below it can be seen the transmitted data and the received data by the ser2par module.Īll the source files for this simulation can be found here. Parallel data thus is an inevitable part in many areas. NEED OF SERIAL TO PARALLEL CONVERTER Parallel communication is essential in many systems. Serial-in parallel-out can be converted to a serial-in serial-out by only considering the last stage. The received data is available in parallel format on the data_outbus.įor the simulation, the Parallel to serial converter is used to generate data and the ser2par receives the data. For N-bit serial to parallel convertor, N number of D flip-flops will be required. If a frame_insignal is detected, the data is latched in and the data_rdyoutput is asserted until the rdinput is asserted by the host.

SERIAL PARALLEL CONVERTER CIRCUIT FSM CODE

In my research, I primarily use R, but I try to use existing code if available. This VHDL module receives serial data from the data_inline. Serial To Parallel Converter Matlab Code For Logistic Regression - 4f33ed1b8f.

0 kommentar(er)

0 kommentar(er)